前回記事はこちら

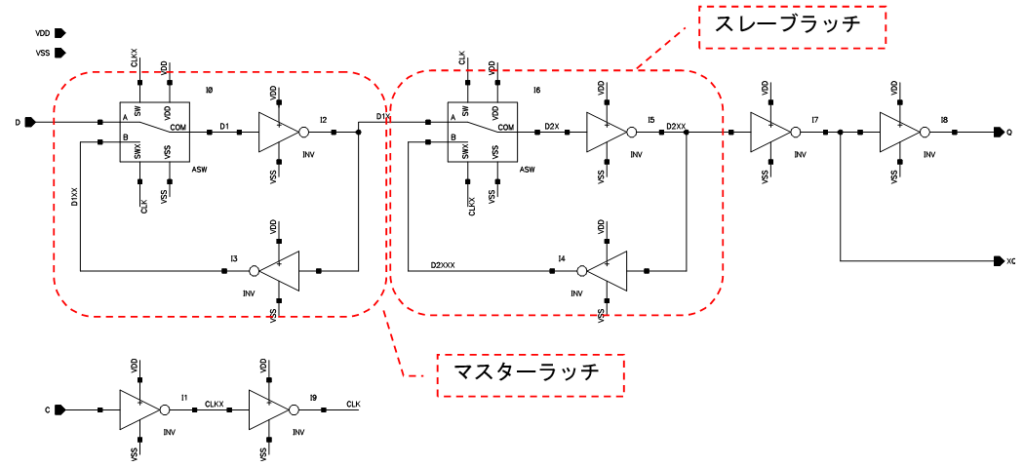

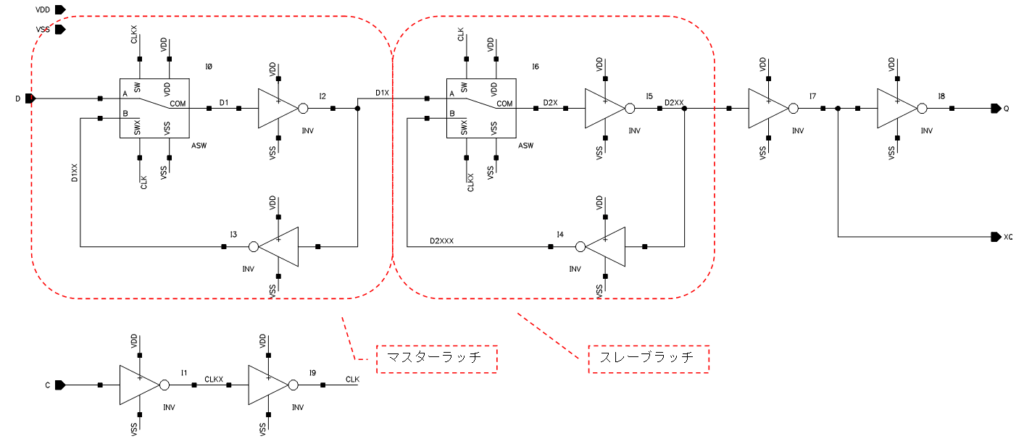

今回は前回紹介したD-FF回路(図 1)の動作を説明したいと思います。

D-FF回路の動作

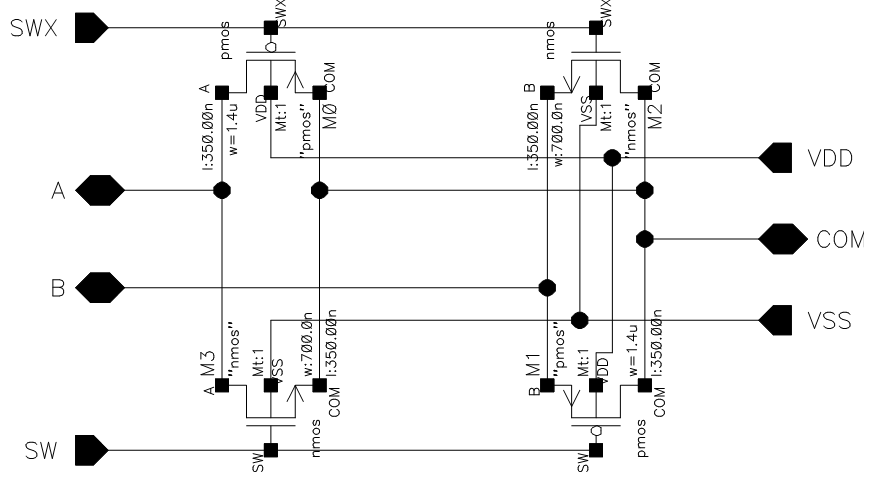

ラッチ内のASW(四角いブロック)の中は下の様になっていて、SW端子が‘H’でSWX端子が‘L’のときは、左側の列のTrがONし右側の列のTrがOFFするので、COM端子はA端子とつながります。逆にSW端子が‘L’でSWX端子が‘H’のときは、COM端子はB端子につながります。

ラッチ内のINV(三角のブロック)はインバータです。

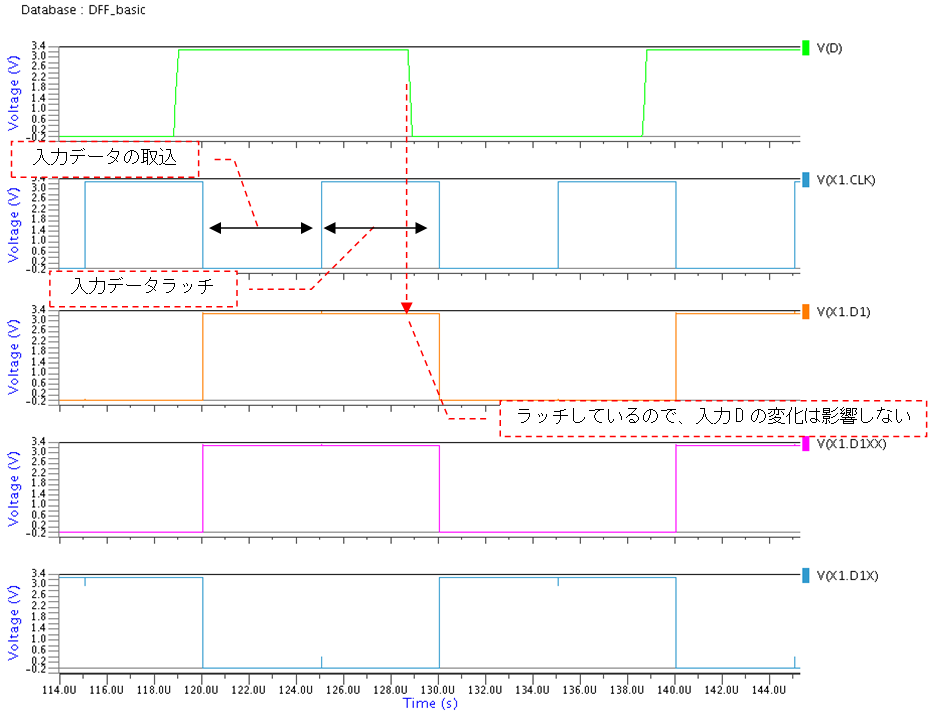

図 1と図 3を使ってマスターラッチの動作から説明します。結構複雑な動きをします(汗)。

マスターラッチの動作

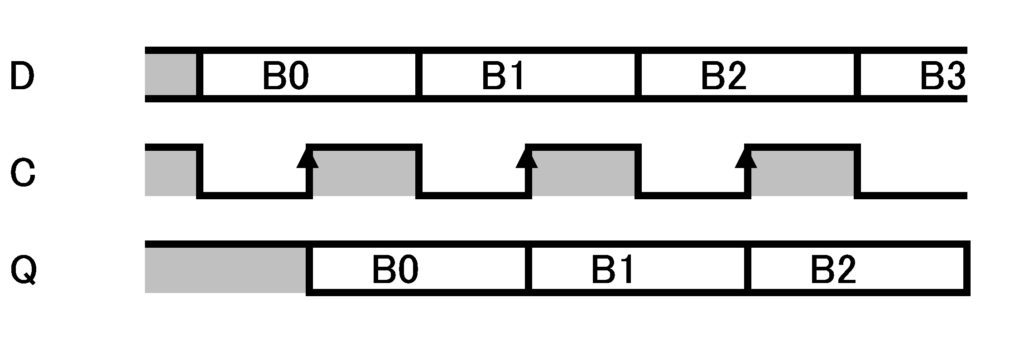

(A)CLKが‘L’の時(つまり、CLKXが‘H’の時):

ASWの端子Aと端子COMが接続し、入力Dが回路内に取り込まれます。

このときD1,D1X,D1XXの状態が変化し、ASWの端子COMからインバータを

2個経由した端子B(つまり、D1XX)は、端子A(つまり入力D)と同じ論理になっています。

(B)CLKが‘H’の時(つまり、CLKXが‘L’の時):

ASWの端子Bと端子COMが接続し、前の状態をラッチします。

つまりD1、D1X、D1XXの正帰還状態となります。

この間、ASWの端子A(つまり入力D)が変化しても、ラッチ回路内は影響を受けません。

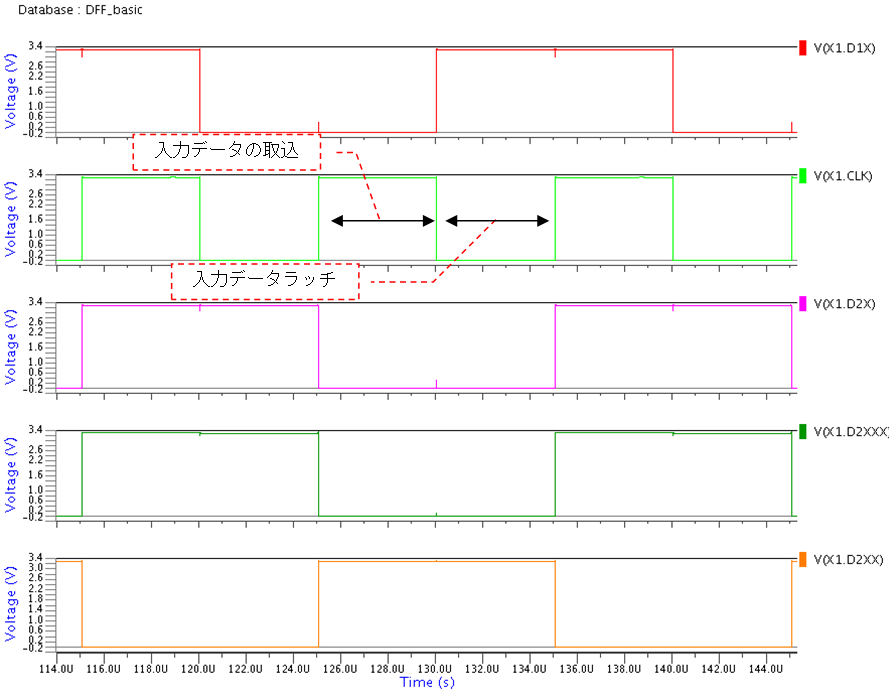

続いて図 1と図 4を使ってスレーブラッチの動作を説明します。

スレーブラッチの動作

(マスターラッチとはCLKの接続が逆になっている事に注意して下さい)

(C)CLKが‘H’の時(つまり、CLKXが‘L’の時):

ASWの端子Aと端子COMが接続し、入力D1Xが回路内に取り込まれます。

このときD2X,D2XX,D2XXXの状態が変化し、ASWの端子COMからインバータを

2個経由した端子B(つまり、D2XXX)は、端子A(つまり入力D)と同じ論理になっています。

(D)CLKが‘L’の時(つまり、CLKXが‘H’の時):

ASWの端子Bと端子COMが接続し、前の状態をラッチします。

このときはD2X,D2XX,D2XXXの正帰還状態となります。

この間、ASWの端子A(つまり入力D)が変化しても、ラッチ回路内は影響を受けません。

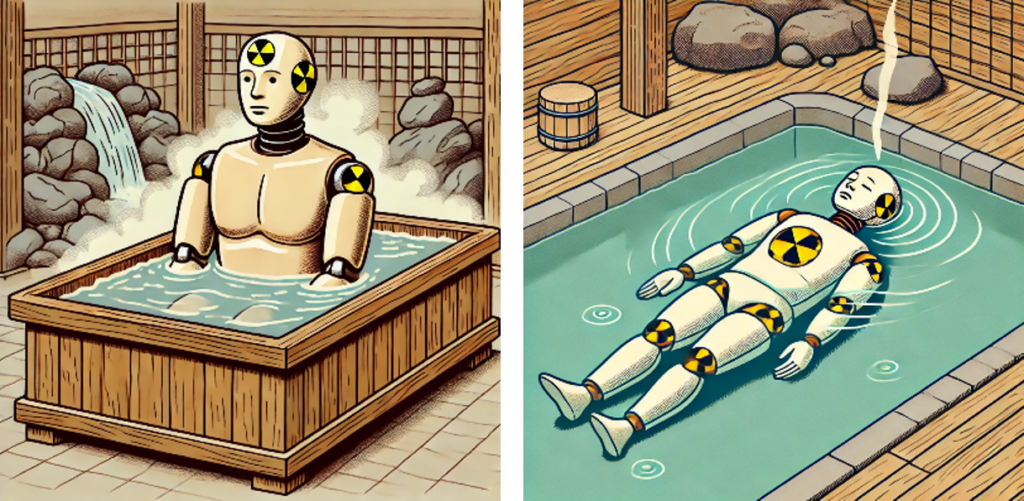

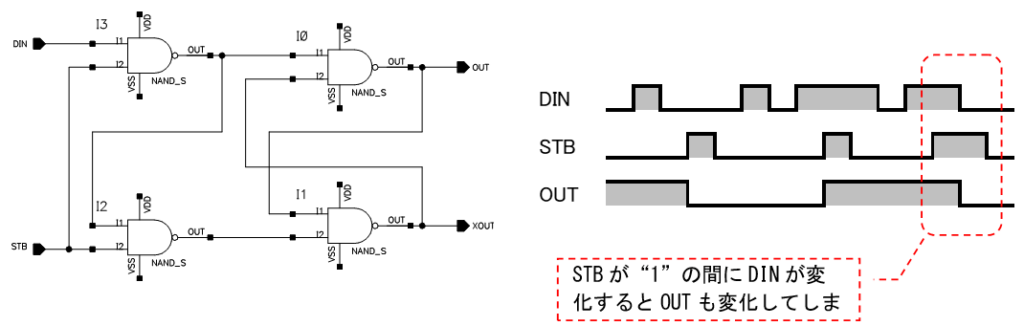

実はこの(D)になる時が一番危険な時なのです。

なぜかというと、“前の状態をラッチする”と“D1Xの変化”がほぼ同時に行われているからです。

安全にするには“前の状態をラッチした後、D1Xが変化する”ようにすれば良いので、

CLKの順番で言うと、

“スレーブラッチのCLKの立下り(CLKXの立ち上がり)の後、マスターラッチのCLKが立下る(CLKXが立ち上がる)”

となります。つまり、スレーブラッチのCLKがいつも早くなるようにしておけば良い事になります。

しかし、実際にはそう単純にはいかない事情があります。

次回はこのあたりをもう少し詳しく紹介したいと思います。