今季節は鬱陶しい梅雨の真っただ中。でも雨上がりの晴れた空に美しい虹がかかっているのを見つけたら、ちょっとうれしく感じます。

アナログ信号とは何か

さてここで、虹について簡単なクイズです。

この写真の虹の色は全部で何色ですか、と問われたらどう答えますか? レインボーカラーの7色?

もし私の小6の息子がそう答えたなら、「うん。でも実際には虹の色はきれいに分かれておらず、連続的に変化してるんだよ、アナログ信号みたいにね。」と答えてしまいます(笑)

虹に例えてみましたが、アナログ信号とは、”時間tに対して変化が連続的な”信号”のことで、関数グラフで表すと図1のような波として表せます。

ディジタル信号処理とは?

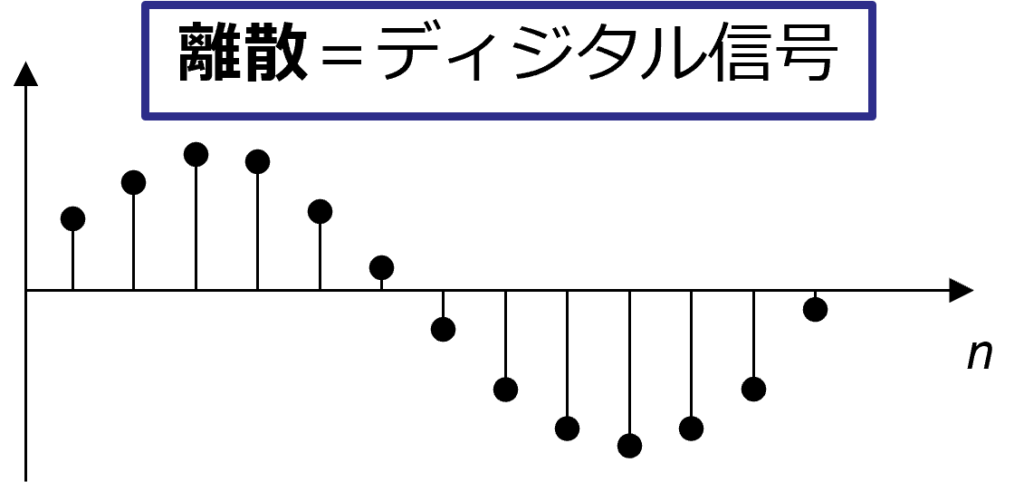

これと対照的なものにディジタル信号があります。

このディジタル(デジタルとも言いますね)とはなんでしょうか?Wikipedia に詳しい解説がありますが、一言で言うならディジタル信号とは、”情報を段階で区切って数字で値nで離散的に示した信号“のことです。

この離散的というのはどういう状態なのか、図2に示しました。図1の連続的なアナログ信号が、段階的に区切られ、切り離された個々の数値になっています。これは、アナログ信号から一定間隔でサンプルを取り出しているのですが、このプロセスを標本化(サンプリング)と呼び、これら標本化された値の集合がディジタル信号となります。

ディジタル信号処理とは、このようにアナログ信号(連続信号)をコンピュータが扱いやすいディジタル信号(離散信号)に変換して、音・映像・通信情報など様々な情報のより高度かつ効率的な処理をコンピュータで実現することです。

実は連続的なアナログ信号はそのまま今のコンピュータでは扱うことはできません。ディジタル信号=離散した数値にしないと処理ができないのです。コンピュータに支えられている今の社会環境にとって、ディジタル信号処理は目立たないけれども、とても重要なプロセスなんです。

ディジタル信号処理を数学的に示すと

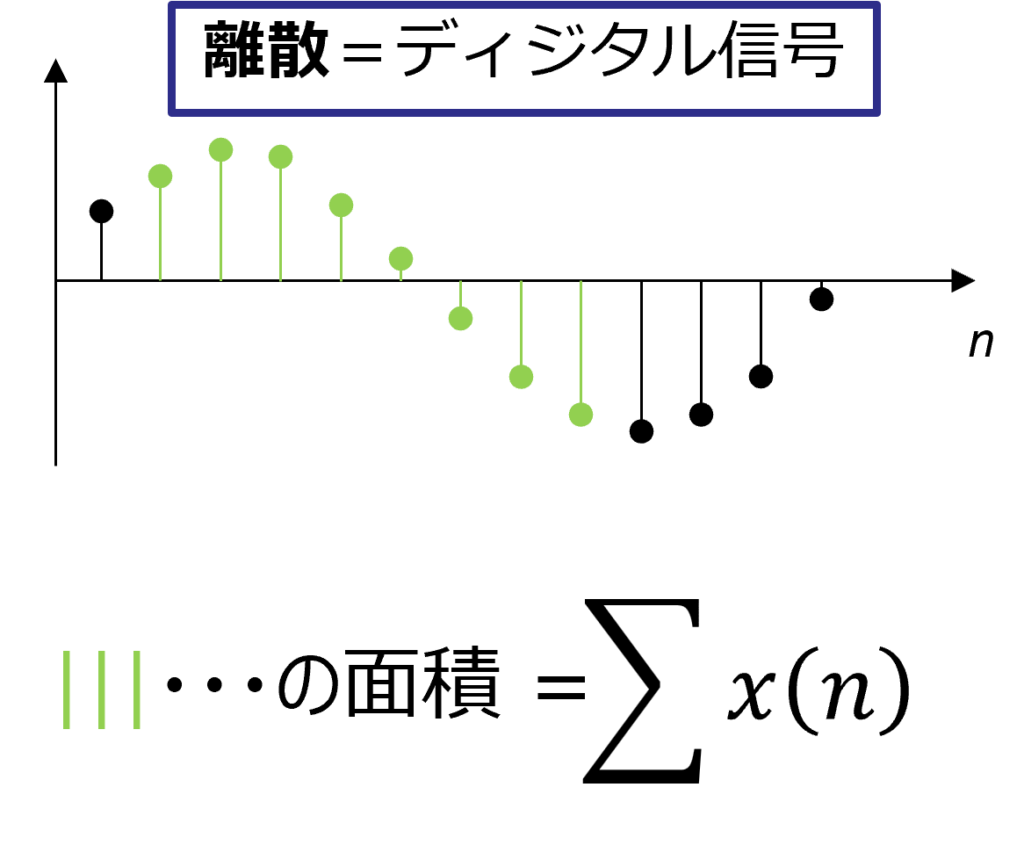

ディジタル信号処理について数学的に示したのが、図3です。

図3

右図の連続=アナログ信号の積分は、時間の関数としての信号の面積を求める操作であり、∫𝑥(𝑡)d𝑡と表されます。これに対して、左図の離散=ディジタル信号では、標本化された値の総和を取ることで、信号の全体的な特性を捉えます。これは∑𝑥(𝑛)という形で表されます。

このとき、ディジタル信号の総和は、アナログ信号の積分に相当すると考えることができます。

ディジタル信号処理を学ぶ意義

ディジタル信号処理は、これまで音声処理、画像処理、通信システムに始まり、私たちが扱う産業機器センサや超音波医療機器など、実に幅広い機器やサービス創出を裏で支えてきました。また私自身、信号処理のプロとして現場で革新的な瞬間を何度も体験しました。その経験から言えるのは「これからエレクトロニクス技術で未来社会を支えていくエンジニアが、信号処理を数学的に理解し適切に扱えるようになれば、技術者として確固たる強みになる」と感じています。

このブログシリーズで、ディジタル信号処理における強力なツールの1つである離散フーリエ変換(DFT)とは何か、高校レベルの数学で理解いただけることを段階を踏んでお伝えしていきます。次回は、フーリエ変換とは何か、そしてその理解の前提条件となる数学知識についてお伝えします。