今回は「PLL(1)」です。

PLLはPhase Locked Loopの略なので、位相がロック(つまり固定した)ループなのです。あらゆる電子器機や機械などPLLを使わない物は無いと言って良いくらい使われています。その基本的な仕組みを何回かに分けて紹介したいと思います。

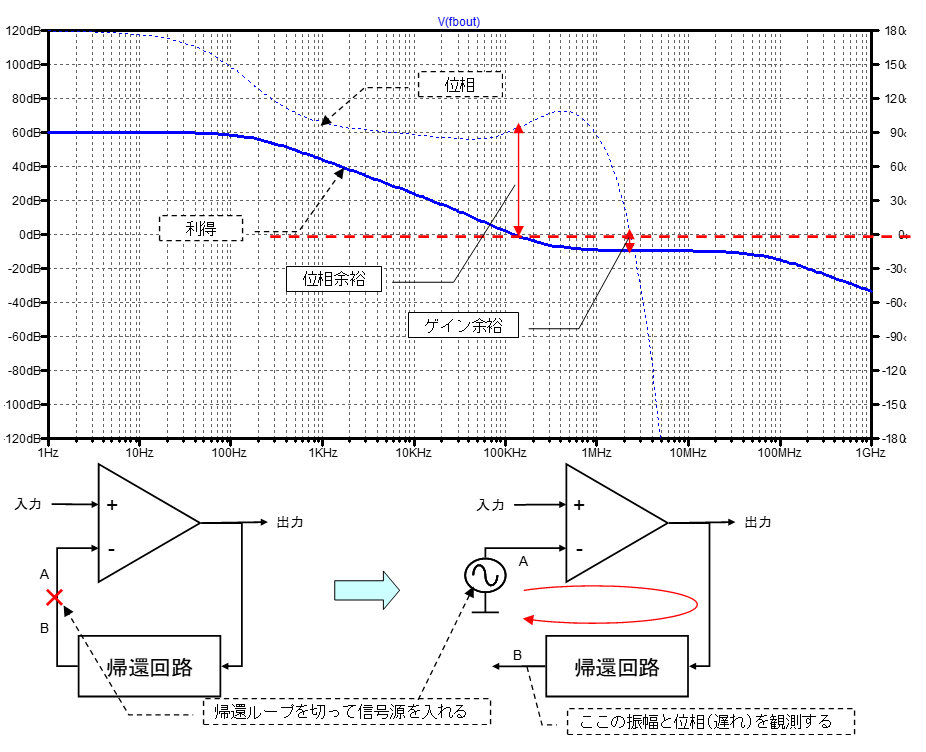

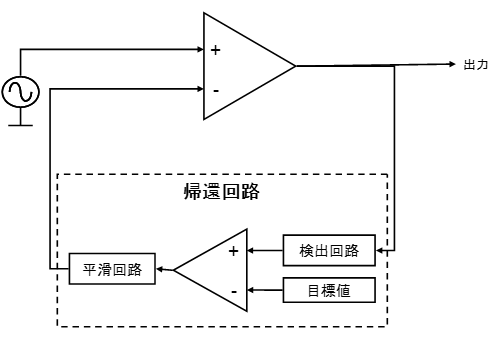

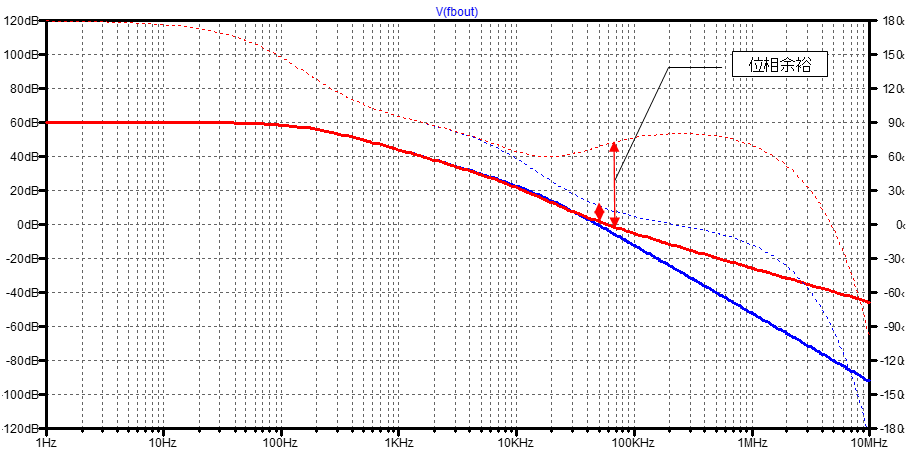

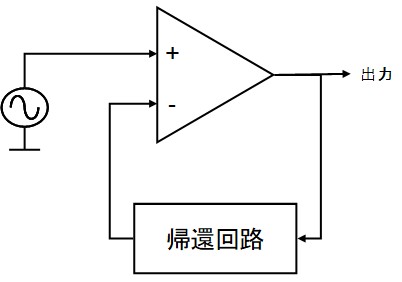

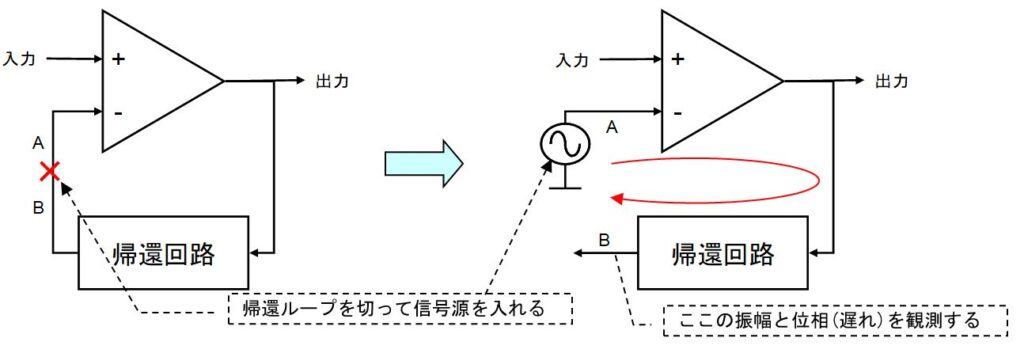

ループって名前がついていることから、PLLはネガティブフィードバックループ(負帰還)の回路方式です。

Phase,つまり位相を固定(Lock)するためのフィードバック回路です。

普通の負帰還回路と何が違うのかというと、扱う対象が”位相”という時間軸のパラメータを扱うことです。

電圧や電流をある基準に合わせる事は想像しやすいですが、位相をある”基準の位相”に合わせる事は想像するのが難しいのではないかと思います。位相や周波数を分かりやすい電圧に置き換えてPLLを説明してみたいと思います。

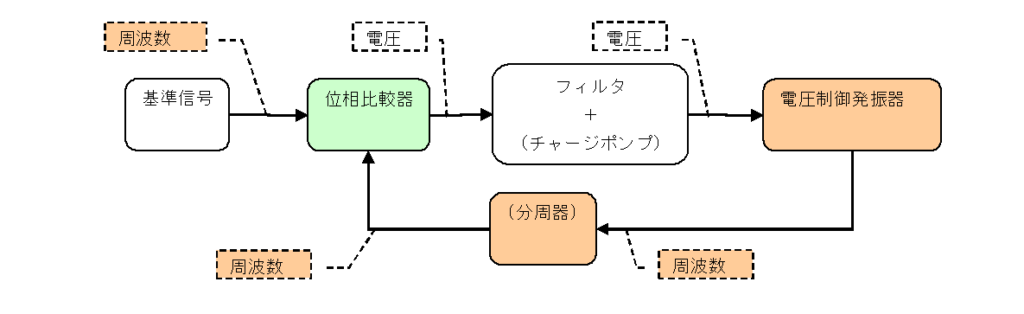

PLLは、位相比較器、フィルタ+チャージポンプ、電圧(または電流)制御発信器、分周器の4つの要素で作る事ができます。

(チャージポンプや分周器はPLLの性能や機能を高めるための回路で、PLLに必須の回路ではありません。)

要素間の接続は上の図のようなのですが、問題なのはその扱う信号(情報)が全て電圧(もしくは電流)ではない事です。

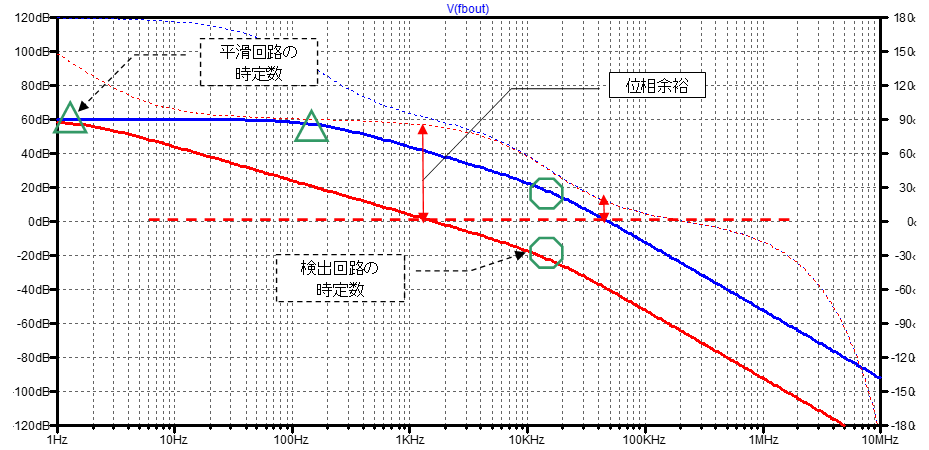

電圧制御発振器から出てくる重要な情報は周波数だし、位相比較器は二つの信号の周波数や位相を比較して電圧に変換します。これらの種類が異なる情報を扱う上で重要なポイントは、”位相は周波数の時間積分”という基本的な法則をどう考えるかです。”位相は周波数の時間積分”とは・・・「1Hz周波数がずれた2つの信号の出力は、1秒後に1周期ずれ、2秒後には2周期、3秒後には・・・と時間と共にドンドンずれる」・・・ということなのですが、当たり前すぎてピンとこないと思います。

位相比較器が行っている事を周波数や位相を電圧に置き換えて考えてみます。

例えば、1MHz=1V、1周期(360°)=1Vと定義します。

1MHz周波数がずれている2つの信号間には1usec後に1周期分のずれが出る事になります。

つまり、”1Vずれた信号を入れた回路の出力が1usec後に1Vになるような回路”にすれば、位相比較が出来る事になります。

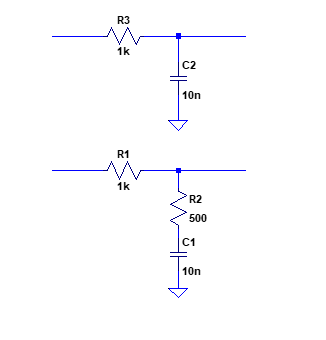

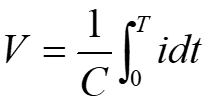

電子回路で上の回路は電流源とコンデンサで意外と簡単に作れます。

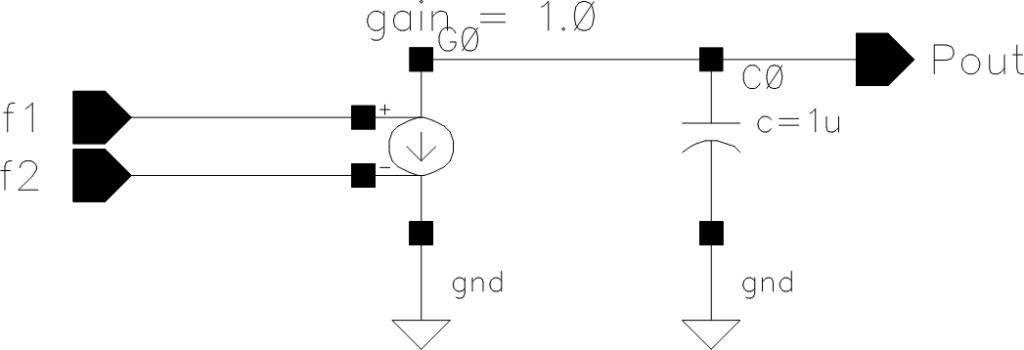

なので、電流をコンデンサに入力すると、時間で積分した結果が電圧として出てきます。回路は下のようになります。

f1とf2に入力した電圧(つまり周波数)差を時間で積分した結果がPoutに出てくるわけですが、差電圧が1V(つまり1MHz)の時、1usec後のPoutは1Vになるように、C0を1uFにしています。

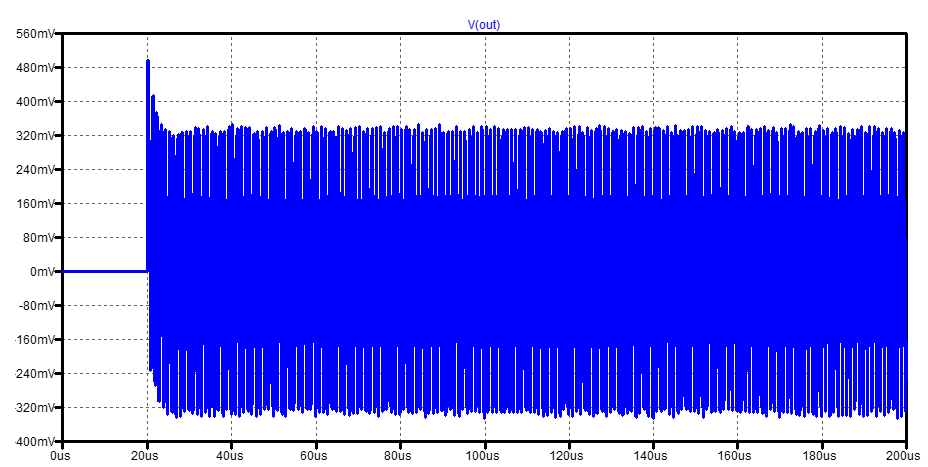

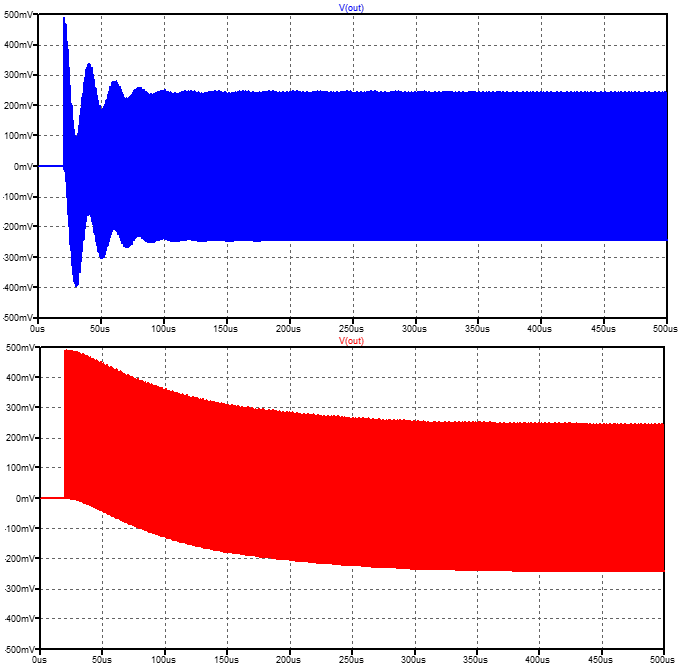

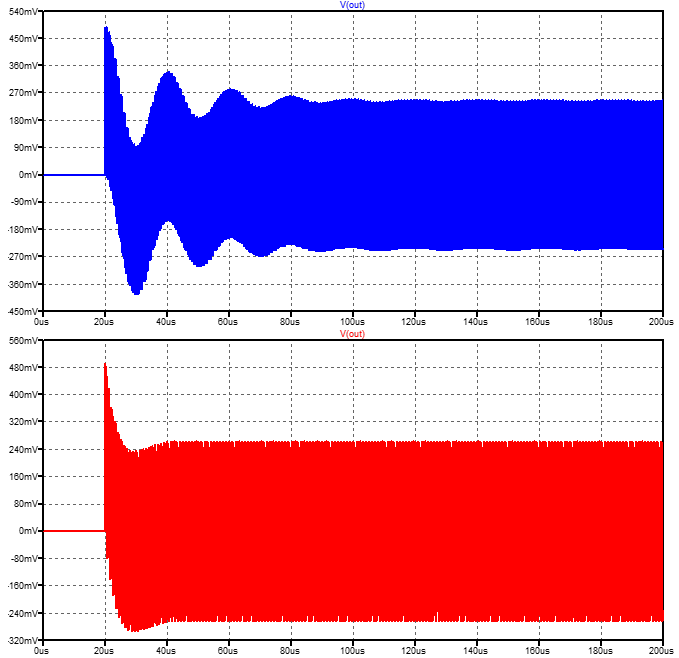

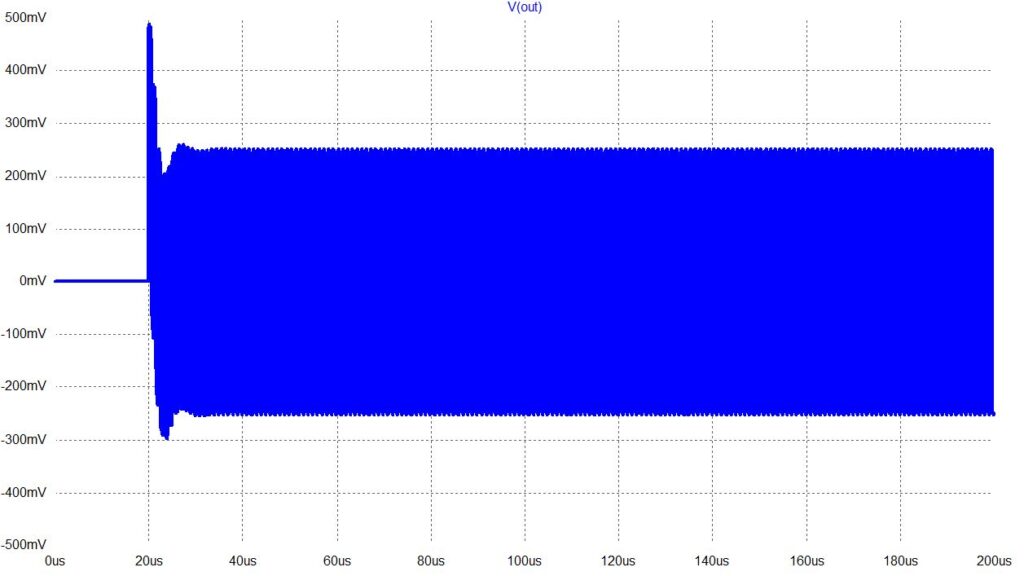

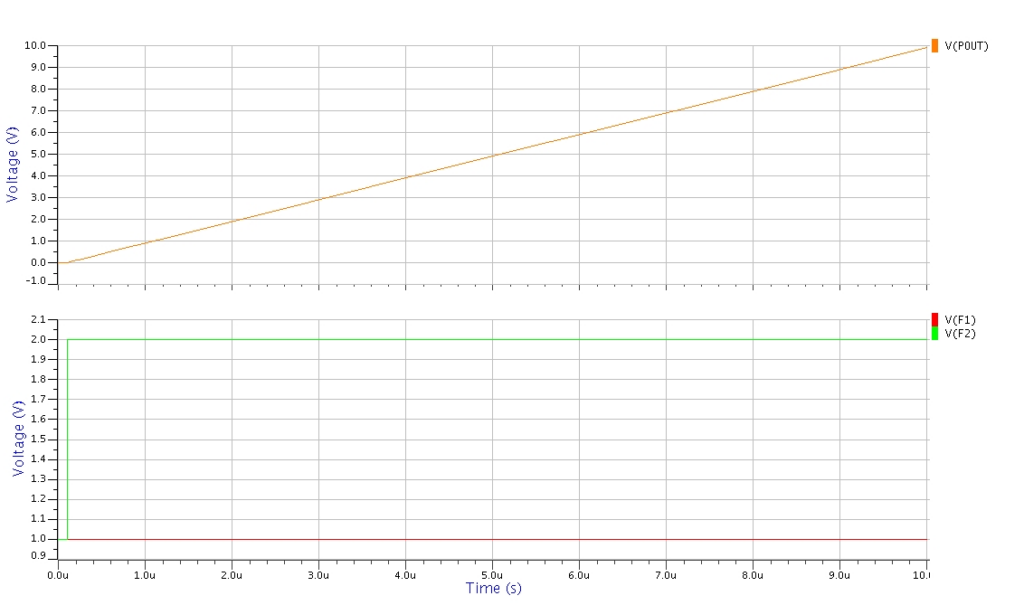

入力に1Vと1.1Vを入力すると・・・

周波数に発生したずれを積分した結果がPoutとして出力されます。

この回路は電源などが無いので、入力に差電圧がある限り出力は無限大まで(計算機がオーバーフローするまで)上がります。

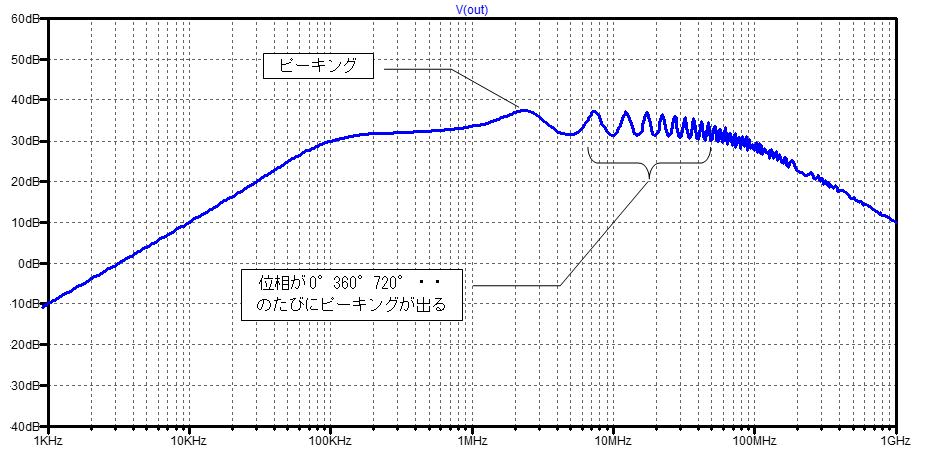

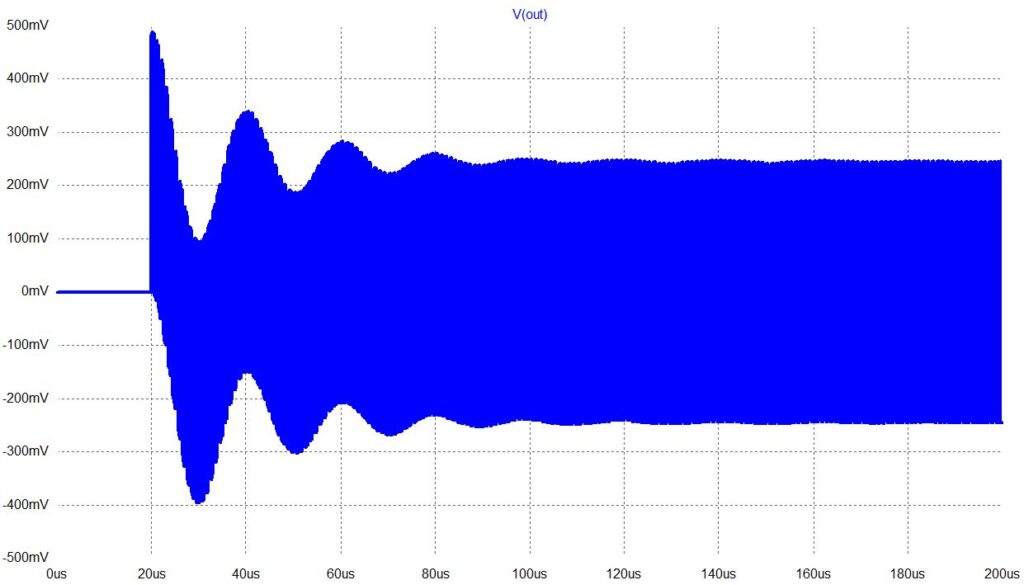

しかし、実際の回路では位相出力電圧は、三角関数やのこぎり波などの繰り返しの波形になります。これは、位相比較器には0°と360°の区別がつかないからです。

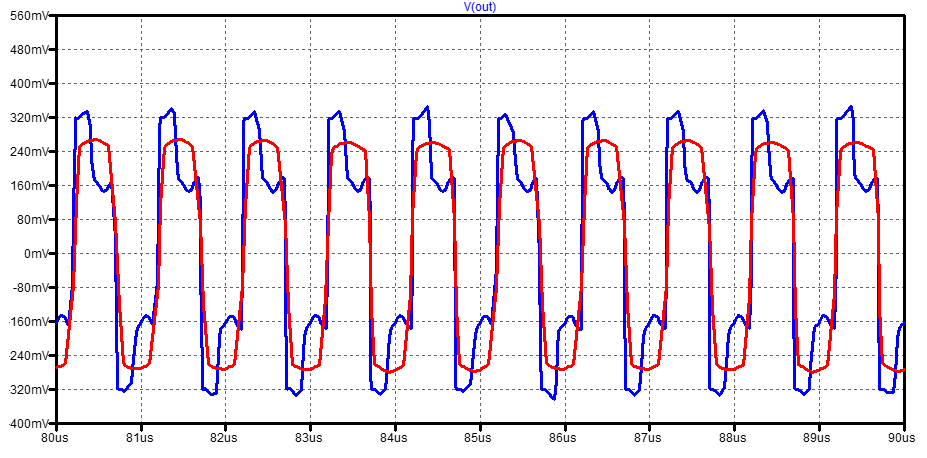

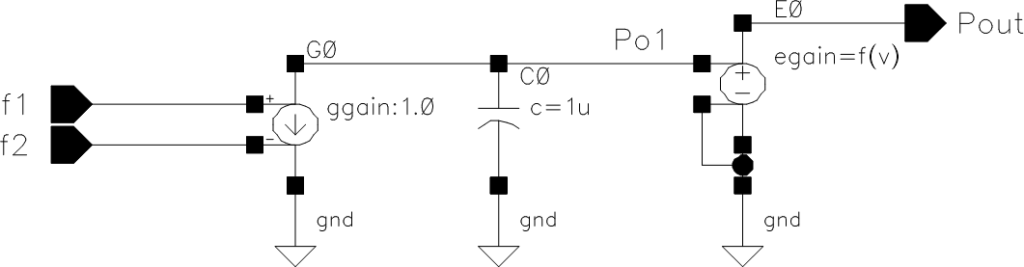

上の回路のE0(電圧依存電圧源)に関数を入れて、出力電圧を細工します。

回路ではうまく出来なかったので、ネットリストを直接いじりました(赤字のところです)

cc0 po1 0 1e-6

gg0 po1 0 f1 f2 1

ee0 pout 0 value=atan(tan(m_pi*v(po1)))/m_pi

余談ですが、CADも便利になって来ているのですが、簡単な変更ならテキストを直接いじったほうが断然早いです。

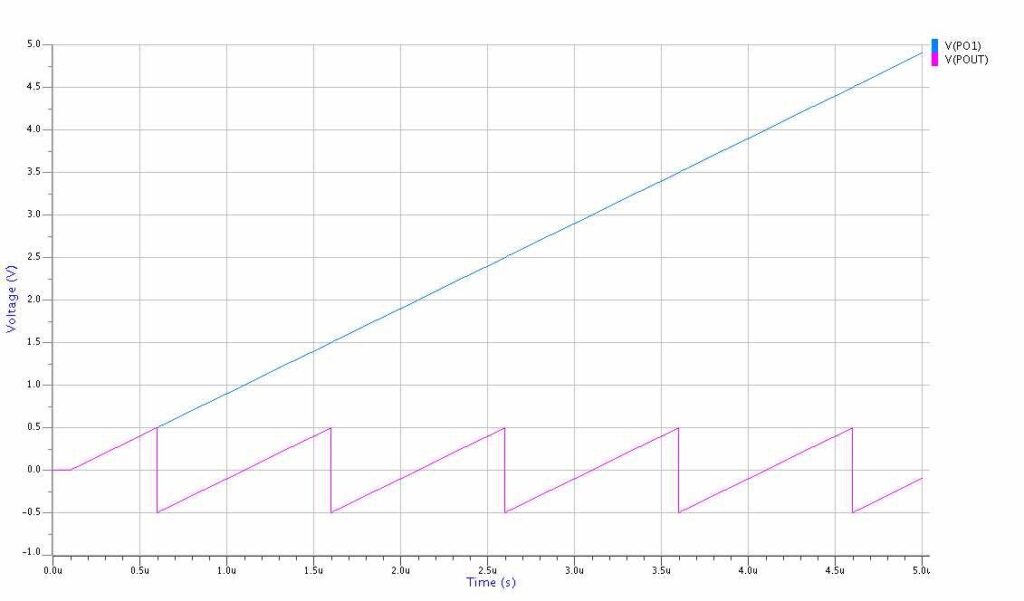

Poutにのこぎり波が出るようになります。

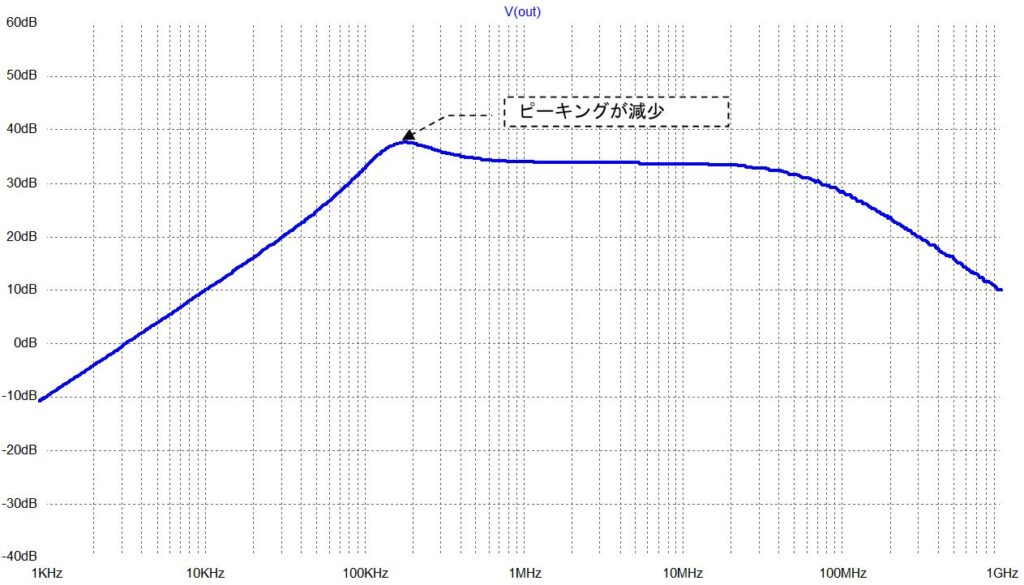

PLLは時間に関連する操作をする回路なので、結構理解しにくし、実回路のまま過渡解析をすると時間がかかる嫌な回路の部類に属しているのですが、ビヘイビアモデルを使うことで、解析時間も短くなるし、理解も簡単になると思います。

次回は、VCOをモデル化して、位相比較器を含めたPLL全体の動作を説明したいと思います。 (美斉津)