今回は「PLL(その3)」です。

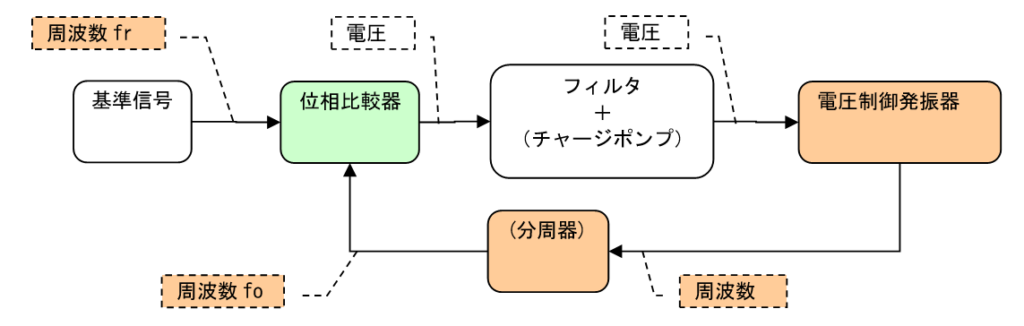

前回はパーツ(位相比較器、VCO)をビヘイビアモデルでモデル化し、PLL全体の周波数特性や過渡解析の例を紹介しました。

今回は、PLL特有の問題(キャプチャーレンジなど)に振れたいと思います。

キャプターレンジ

実験室で”PLLがロックしない”といった叫びを聴いたことがあるでしょうか?僕は何度も叫びました。

では、なぜPLLがロックできないかと言うとそれば「位相比較器に入力される2つに信号の周波数差にフィルタが応答できない」からです。

別の言葉で言うと、周波数差がキャプチャーレンジより大きいとPLLは引き込めなくなってしまいます。

PLLに関する文献は山ほどあるので、キャプチャーレンジの計算は文献にまかせて、PLLが引き込めていない時には何が起きているのかを今までのビヘイビアモデルを使って調べてみたいと思います。

過渡解析を使った検証

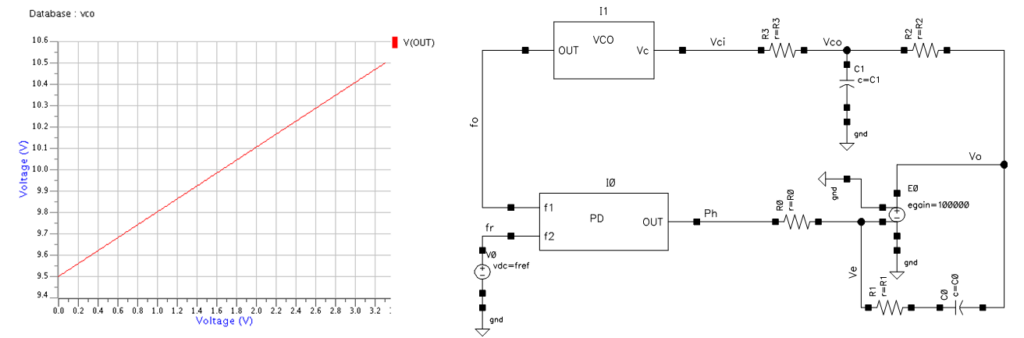

前回のVCOとPLL回路を今回も使います。回路定数も前回と同じで先ずは、

.param r0=510 r1=10k c0=1n r2=1k c1=10pとします。

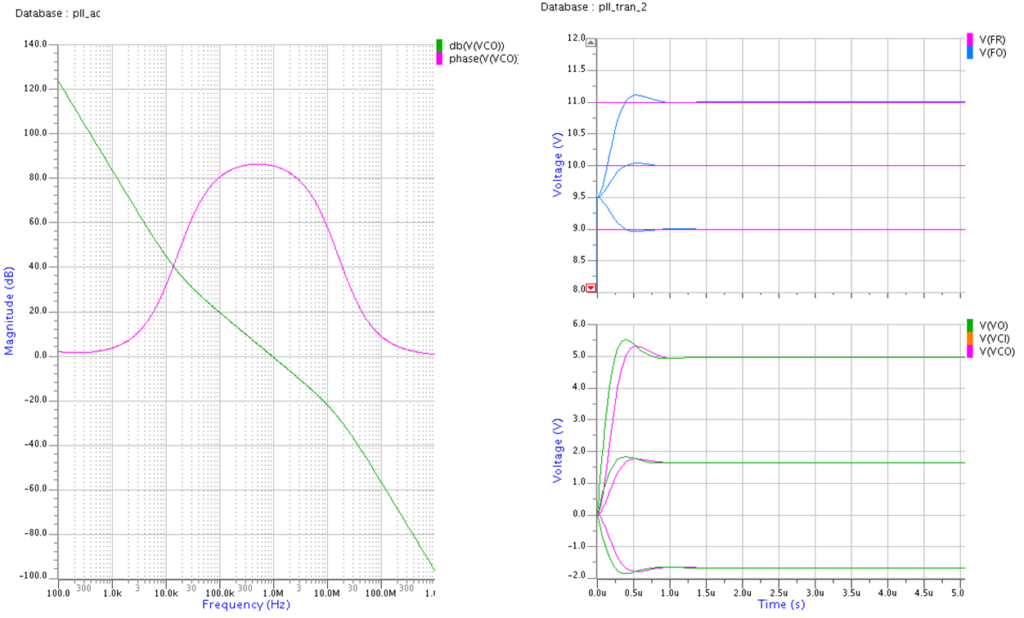

この回路定数だと位相余裕も十分だし、入力する周波数frを9,10,11MHzとした場合のどれでも1.5usec程度で引き込めている事が過渡解析で分かります。

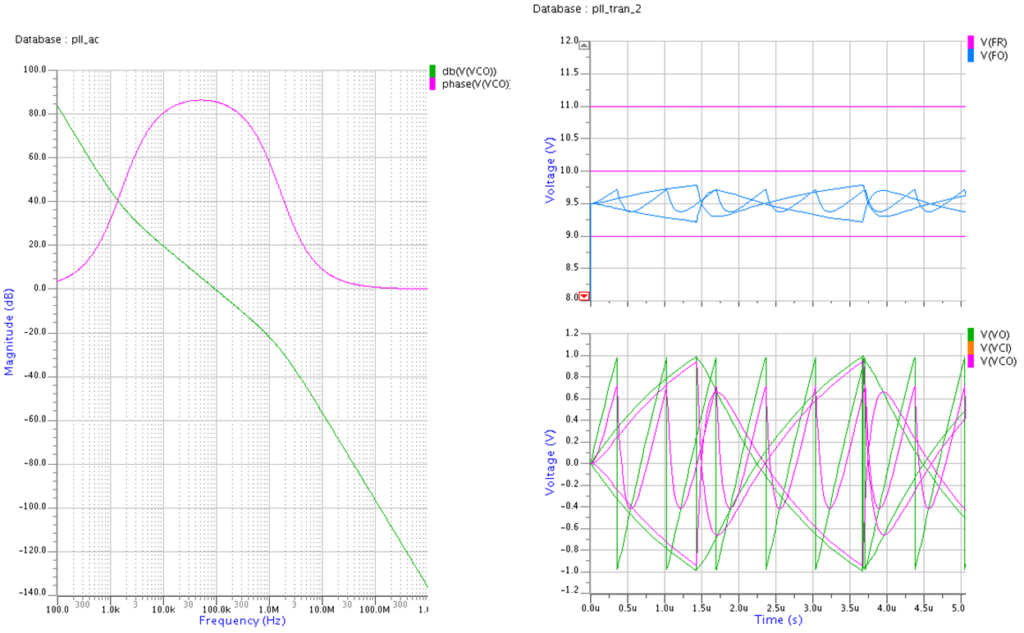

では、フィルタ時定数を変更(注1)してゲイン特性が0dBとなる周波数を1桁遅くした時にどうなるか調べてみると・・・・

注1).param r0=510 r1=1k c0=100n r2=1k c1=100p

位相余裕などは十分取れているので問題は無いのですが、過渡解析は”PLLがロックしない”と叫んでいます!

なぜPLLがロックしないのか?

フィルタの時定数を変更したことで、位相比較器のビート信号(差周波数で振動する)をVCOに伝達できず、VCO制御電圧が十分振れずにVCO出力周波数が目標周波数に到達できないために、PLLが引き込めなくなってしまっています。

PLLを使ってジッタを抑圧する時にはPLLの帯域は狭いほう都合がいいので、ゲイン特性が0dBとなる周波数をなるべく低く設定しようとします・・・・そして、上のように罠にはまってしまうのです。

あらゆる電子回路で使われているPLLですが、確実に動く設計をするにはAC解析だけでは不十分で、必ず過渡解析が必要になります。しかし実際の回路をそのまま過渡解析に使っていたら莫大な時間が必要になり、非現実的です。そんな時に便利なビヘイビアモデルを紹介しました。

次回はエミッタ接地やソース接地の増幅器についての予定です。(美斉津)

コメント

この記事へのコメントの受付は締め切りました。